**SoC Blockset™**

Reference

# MATLAB&SIMULINK®

#### **How to Contact MathWorks**

Latest news: www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

**T**

Phone: 508-647-7000

The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

SoC Blockset™ Reference

© COPYRIGHT 2019-2023 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

$MathWorks\ products\ are\ protected\ by\ one\ or\ more\ U.S.\ patents.\ Please\ see\ www.mathworks.com/patents\ for\ more\ information.$

#### **Revision History**

| March 2019     | Online Only | New for Version 1.0 (Release 2019a)     |

|----------------|-------------|-----------------------------------------|

| September 2019 | Online only | Revised for Version 1.1 (Release 2019b) |

| March 2020     | Online only | Revised for Version 1.2 (Release 2020a) |

| September 2020 | Online only | Revised for Version 1.3 (Release 2020b) |

| March 2021     | Online only | Revised for Version 1.4 (Release 2021a) |

| September 2021 | Online only | Revised for Version 1.5 (Release 2021b) |

| March 2022     | Online only | Revised for Version 1.6 (Release 2022a) |

| September 2022 | Online only | Revised for Version 1.7 (Release 2022b) |

| March 2023     | Online only | Revised for Version 1.8 (Release 2023a) |

## Contents

## Blocks

1

## **Configuration Parameters**

2

| Hardware Implementation Pane          | 2-2           |

|---------------------------------------|---------------|

| Hardware Implementation Pane Overview | 2-2           |

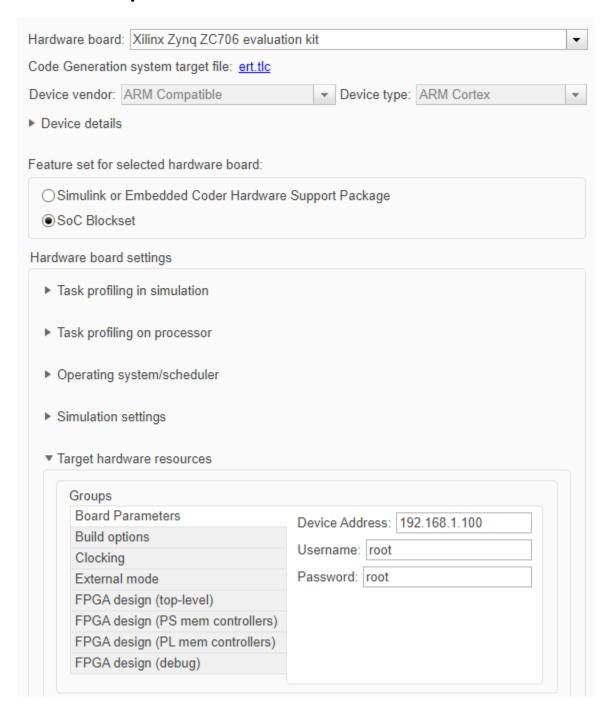

| Hardware board settings               | 2-3           |

| Design Mapping                        | 2-3           |

| Task profiling in simulation          | 2-3           |

| Task profiling on processor           | 2-3           |

| Operating system/scheduler            | 2-4           |

| Simulation Settings                   | 2-4           |

| Board Parameters                      | 2-4           |

| Processor                             | 2-4           |

| Board Options                         | 2-4           |

| Clocking                              | 2-5           |

| External Mode                         | 2-5           |

| FPGA design (top-level)               | 2-5           |

| FPGA design (PS mem controllers)      | 2-5<br>2-6    |

|                                       |               |

| FPGA design (PL mem controllers)      | 2-6           |

| FPGA design (mem channels)            | 2-7           |

| FPGA design (debug)                   | 2-7           |

| Hardware Board Settings               | 2-8           |

| Processing Unit                       | 2-8           |

| Trocessing Olint                      | 2-0           |

| Design Mapping                        | 2-9           |

| View/Edit Hardware Mapping            | 2-9           |

| view/Edit Hardware Mapping            | 4-9           |

| Task Profiling in Simulation          | 2-10          |

| Show in SDI                           | 2-10          |

| Save to file                          | 2-10          |

| Overwrite file                        | 2-10          |

| Overwrite me                          | 2-10          |

| Task Profiling on Processor           | 2-11          |

| Show in SDI                           | 2-11          |

| Save to file                          | 2-11          |

| Overwrite file                        | 2-11          |

| Instrumentation                       | 2-11          |

| Profiling duration                    | 2-11          |

| 1 forming duration                    | <u> 2</u> -11 |

| Operating System/Scheduler         Kernel latency                                                                                                                                                                                                                             | 2-1<br>2-1                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Simulation Settings Set random number generator seed Seed Value Cache input data at task start                                                                                                                                                                                | 2-1<br>2-1<br>2-1<br>2-1                      |

| Processor                                                                                                                                                                                                                                                                     | 2-1<br>2-1                                    |

| Board Parameters  Device Address  Username Password                                                                                                                                                                                                                           | 2-1<br>2-1<br>2-1<br>2-1                      |

| Clocking                                                                                                                                                                                                                                                                      | 2-1<br>2-1                                    |

| Build Action                                                                                                                                                                                                                                                                  | 2-1<br>2-1                                    |

| External Mode  Communication Interface  Run external mode in a background thread  Port  Verbose                                                                                                                                                                               | 2-1<br>2-1<br>2-1<br>2-1<br>2-2               |

| FPGA design (top-level)  View/Edit Memory Map  Include 'MATLAB as AXI Master' IP for host-based interaction  Include processing system  Interrupt latency (s)  Register configuration clock frequency (MHz)  IP core clock frequency (MHz)                                    | 2-2<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2 |

| FPGA design (mem controllers)  Controller clock frequency (MHz)  Controller data width (bits)  Bandwidth derating (%)  First write transfer latency (clocks)  Last write transfer latency (clocks)  First read transfer latency (clocks)  Last read transfer latency (clocks) | 2-2<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2 |

| FPGA design (mem channels)  Interconnect clock frequency (MHz)  Interconnect data width (bits)  Interconnect FIFO depth (num bursts)  Interconnect almost-full depth                                                                                                          | 2-2<br>2-2<br>2-2<br>2-2<br>2-2               |

| FPGA design (debug)  Memory channel diagnostic level  Include AXI interconnect monitor  Trace capture depth                                                                                                                                                                   | 2-2<br>2-2<br>2-2<br>2-2                      |

| Functions                                                                           |     |

|-------------------------------------------------------------------------------------|-----|

| Objects                                                                             |     |

| Tools                                                                               | •   |

| 10013                                                                               |     |

| Blocks                                                                              |     |

| Coder Target Context Sensitive Help                                                 | ' [ |

| eters       7-2         n Pane Overview       7-2          7-3         es       7-4 |     |

|                                                                                     |     |

| 7-7 7-7 7-7 7-7 7-7 7-7 7-8 7-8 7-8                                                 |     |

| 7-9 7-9 7-9 atic library 7-9 7-10 and file 7-11                                     |     |

7-11

| locking                   |           | <br> |  |

|---------------------------|-----------|------|--|

| External oscillator (MHz) |           |      |  |

| CPU Clock (MHz)           |           | <br> |  |

| onnectivity               |           | <br> |  |

| Connectivity interface    |           |      |  |

| Port                      |           |      |  |

| Baudrate                  | . <b></b> | <br> |  |

Tools

8

## **Blocks**

## **SoC Bus Creator**

Convert control signals to bus

#### Libraries:

SoC Blockset / Hardware Logic Connectivity

## **Description**

The SoC Bus Creator block combines a set of signals into a bus. The block accepts control signals and outputs a bus.

You can configure this block to support multiple protocol interface types. Parameter and port configurations for this block vary based on your desired protocol interface type and mode of operation, as outlined in this table.

| Protocol<br>Interface<br>Type | Mode of<br>Operation | Parameter Configuration                                                             | Enabled Input Ports |

|-------------------------------|----------------------|-------------------------------------------------------------------------------------|---------------------|

| Data stream                   | Read data stream     | Set Control protocol to Data stream and Control type to Ready.                      | ready               |

|                               | Write data stream    | Set <b>Control protocol</b> to Data                                                 | valid               |

|                               |                      | stream and <b>Control type</b> to Valid.                                            | tlast               |

| Pixel stream                  | Read video stream    | Set Control protocol to Pixel stream and Control type to Ready.                     | ready               |

|                               | Write video stream   | Set <b>Control protocol</b> to Pixel stream and <b>Control type</b> to Valid.       | hStart              |

|                               |                      |                                                                                     | hEnd                |

|                               |                      |                                                                                     | vStart              |

|                               |                      |                                                                                     | vEnd                |

|                               |                      |                                                                                     | valid               |

|                               | Read video stream    | Set Control protocol to Pixel                                                       | ready               |

|                               | with frame sync      | Ready frame with sync.                                                              | fsync               |

| Random                        | Read data            | Set <b>Control protocol</b> to Random access read and <b>Control type</b> to Ready. | rd_addr             |

| access read                   |                      |                                                                                     | rd_len              |

|                               |                      | io neady.                                                                           | rd_avalid           |

|                               |                      |                                                                                     | rd_dready           |

| Protocol<br>Interface<br>Type | Mode of<br>Operation | Parameter Configuration                        | Enabled Input Ports |

|-------------------------------|----------------------|------------------------------------------------|---------------------|

| Random                        |                      | l <del>-</del>                                 | wr_addr             |

| access write                  |                      | access write and <b>Control type</b> to Valid. | wr_len              |

|                               |                      | to vacta.                                      | wr_valid            |

#### **Ports**

#### Input

valid — Valid control signal

boolean scalar

Valid control signal, specified as a scalar. You can use this port for data stream and pixel stream protocols only.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to either Data stream or Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

tlast — Indication of end of data packet

boolean scalar

Indication of end of the data packet, specified as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Data stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### ready — Ready control signal

boolean scalar

Ready control signal, specified as a Boolean scalar. This port is available for Data stream and Pixel stream control protocols.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to either Data stream or Pixel stream and the **Control type** parameter to Ready or Ready with frame sync.

Data Types: Boolean

**hStart** — First pixel in horizontal line of frame

boolean scalar

First pixel in a horizontal line of a frame, specified as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### **hEnd** — Last pixel in horizontal line of frame

boolean scalar

Last pixel in a horizontal line of a frame, specified as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### vStart — First pixel in first (top) line of frame

boolean scalar

First pixel in the first (top) line of a frame, specified as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### vEnd — Last pixel in last (bottom) line of frame

boolean scalar

Last pixel in the last (bottom) line of a frame, specified as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### **fsync** — Frame synchronization

boolean scalar

Frame synchronization, specified as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Ready with frame sync.

Data Types: Boolean

#### rd addr — Reader address

scalar

Reader address, specified as a scalar. It is the starting address for the read transaction that is sampled at the first cycle of the transaction.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access read.

Data Types: uint32

#### rd\_len — Reader data length

scalar

Reader data length, specified as a scalar. It means the number of data values that you want to read, sampled at the first cycle of the transaction.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access read.

Data Types: uint32

#### rd\_avalid — Reader valid status

boolean scalar

Reader valid status, specified as a Boolean scalar. It indicates whether the read request is valid.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access read.

Data Types: Boolean

#### rd\_dready — Reader ready status

boolean scalar

Reader ready status, specified as a Boolean scalar. It indicates when the hardware logic can start accepting data.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access read.

Data Types: Boolean

#### **wr\_addr** — Writer address

scalar

Specify the starting address to which the hardware writes.

#### **Dependencies**

To enable this port, set the Control protocol parameter to Random access write.

Data Types: uint32

#### wr\_len — Writer data length

scalar

Specify the number of data elements in the write transaction.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access write.

Data Types: uint32

#### wr\_valid — Writer valid data

boolean scalar

Writer valid data, specified as a scalar. It indicates the data signal sampled at the output is valid.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access write.

Data Types: Boolean

#### Output

#### ctrlBus — Output control bus

bus

Output control bus, returned as a bus.

The data type of the output control bus depends on the values of the **Control protocol** and **Control type** parameters.

| Parameter Configuration                                                              | Output Data Type          |

|--------------------------------------------------------------------------------------|---------------------------|

| Set Control protocol to Data stream and Control type to Ready.                       | StreamS2MBus0bj           |

| Set <b>Control protocol</b> to Data stream and <b>Control type</b> to Valid.         | StreamM2SBusObj           |

| Set <b>Control protocol</b> to Pixel stream and <b>Control type</b> to Ready.        | StreamVideoS2MBusObj      |

| Set Control protocol to Pixel stream and Control type to Valid.                      | pixelcontrol              |

| Set Control protocol to Pixel stream and Control type to Ready frame with sync.      | StreamvideoFsyncS2MBusObj |

| Set <b>Control protocol</b> to Random access read and <b>Control type</b> to Ready.  | ReadControlM2SBusObj      |

| Set <b>Control protocol</b> to Random access write and <b>Control type</b> to Valid. | WriteControlM2SBusObj     |

Data Types: StreamS2MBusObj | StreamM2SBusObj | StreamVideoS2MBusObj | pixelcontrol | StreamvideoFsyncS2MBusObj | ReadControlM2SBusObj | WriteControlM2SBusObj

#### **Parameters**

#### **Control protocol** — Protocol interface selection

Data stream (default) | Pixel stream | Random access read | Random access write

Specify the protocol interface as one of these values:

- Data stream Use this protocol if you require AXI4 data stream.

- Pixel stream Use this protocol if you require AXI4 video stream.

- Random access read Use this protocol if you require AXI4 read.

- Random access write Use this protocol if you require AXI4 write.

The input ports of the block vary based on the type of **Control protocol** and **Control type** that you select. For more details, see "Description" on page 1-2.

#### **Control type** — Control type selection

Valid (default) | Ready | Ready with frame sync

Specify the type of control.

To enable the Ready with frame sync option, set the **Control protocol** parameter to Pixel stream.

The input ports of the block vary based on the type of **Control protocol** and **Control type** that you select. For more details, see "Description" on page 1-2.

## **Version History**

Introduced in R2019a

#### **Extended Capabilities**

#### **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

#### **Fixed-Point Conversion**

Design and simulate fixed-point systems using Fixed-Point Designer™.

#### See Also

SoC Bus Selector

## **SoC Bus Selector**

Convert bus to control signals

#### Libraries

SoC Blockset / Hardware Logic Connectivity

## **Description**

The SoC Bus Selector block converts a set of control signals from a bus. The block accepts a bus and outputs control signals.

You can configure this block to support multiple protocol interface types. Parameter and port configurations for this block vary based on your desired protocol interface type and mode of operation, as outlined in this table.

| Protocol<br>Interface Type | Mode of Operation  | Parameter<br>Configuration                                      | Enabled Output Ports |

|----------------------------|--------------------|-----------------------------------------------------------------|----------------------|

| Data stream                | Read stream data   | Set Control protocol to                                         | valid                |

|                            |                    | Data stream and Control type to Valid.                          | tlast                |

|                            | Write stream data  | Set Control protocol to Data stream and Control type to Ready.  | ready                |

| Pixel stream               | Read video stream  | Set Control protocol to                                         | hStart               |

|                            |                    | Pixel stream and Control type to Valid.                         | hEnd                 |

|                            |                    | Control type to vaciu.                                          | vStart               |

|                            |                    |                                                                 | vEnd                 |

|                            |                    |                                                                 | valid                |

|                            | Write video stream | Set Control protocol to Pixel stream and Control type to Ready. | ready                |

| Random access              | Read data          | Set Control protocol to                                         | rd_aready            |

| read                       |                    | Random access read and <b>Control type</b> to Valid.            | rd_dvalid            |

| Random access              | Write data         | Set Control protocol to                                         | wr_ready             |

| write                      |                    | Random access write and <b>Control type</b> to                  | wr_bvalid            |

|                            |                    | Ready.                                                          | wr_complete          |

#### **Ports**

#### Input

**ctrlBus** — Input control bus

hus

Input control bus, specified as a bus.

The data type of the input control bus depends on the values of the **Control protocol** and **Control type** parameters.

| Parameter Configuration                                                              | Input Data Type       |

|--------------------------------------------------------------------------------------|-----------------------|

| Set Control protocol to Data stream and Control type to Valid.                       | StreamM2SBusObj       |

| Set <b>Control protocol</b> to Data stream and <b>Control type</b> to Ready.         | StreamS2MBus0bj       |

| Set <b>Control protocol</b> to Pixel stream and <b>Control type</b> to Valid.        | pixelcontrol          |

| Set Control protocol to Pixel stream and Control type to Ready.                      | StreamVideoS2MBusObj  |

| Set <b>Control protocol</b> to Random access read and <b>Control type</b> to Valid.  | ReadControlS2MBus0bj  |

| Set <b>Control protocol</b> to Random access write and <b>Control type</b> to Ready. | WriteControlS2MBusObj |

Data Types: StreamM2SBusObj | StreamS2MBusObj | pixelcontrol | StreamVideoS2MBusObj | ReadControlS2MBusObj | WriteControlS2MBusObj

#### Output

valid — Valid control signal

boolean scalar

Valid control signal, returned as a scalar. You can use this port for data stream and pixel stream protocols only.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to either Data stream or Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

tlast — Indication of end of data packet

boolean scalar

Indication of end of the data packet, returned as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Data stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### ready — Ready control signal

boolean scalar

Ready control signal, returned as a Boolean scalar. This port is available for Data stream and Pixel stream control protocols.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to either Data stream or Pixel stream and the **Control type** parameter to Ready.

Data Types: Boolean

#### **hStart** — First pixel in horizontal line of frame

boolean scalar

First pixel in a horizontal line of a frame, returned as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### **hEnd** — Last pixel in horizontal line of frame

boolean scalar

Last pixel in a horizontal line of a frame, returned as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### **vStart** — First pixel in first (top) line of frame

boolean scalar

First pixel in the first (top) line of a frame, returned as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### **vEnd** — Last pixel in last (bottom) line of frame

boolean scalar

Last pixel in the last (bottom) line of a frame, returned as a Boolean scalar.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Pixel stream and the **Control type** parameter to Valid.

Data Types: Boolean

#### rd\_aready — Accept read requests

boolean scalar

Accept read requests, returned as a scalar. It indicates when to accept read requests.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access read.

Data Types: Boolean

#### rd dvalid — Read request valid

boolean scalar

Read request valid, returned as a Boolean scalar. It is the control signal that indicates the data returned from the read request is valid.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access read.

Data Types: Boolean

#### wr\_ready — Write ready signal

boolean scalar

Write ready signal, returned as a Boolean scalar. It corresponds to the backpressure from the slave IP core or external memory. When this value is 1 (high), it indicates that data can be sent. When this value is 0 (low), it indicates that the hardware logic must stop sending data within one clock cycle.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access write.

Data Types: Boolean

#### wr\_bvalid — Write valid signal

boolean scalar

Write valid signal, returned as a Boolean scalar. It is the response signal from the slave IP core that you can use for diagnosis purposes. This value becomes 1 (high) after the AXI4 interconnect accepts each burst transaction.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access write.

Data Types: Boolean

#### wr\_complete — Write transaction complete

boolean scalar

Write transaction complete, specified as a Boolean scalar. It is the control signal that when remains high for one clock cycle indicates that the write transaction has completed. This signal asserts at the last wr\_bvalid of the burst.

#### **Dependencies**

To enable this port, set the **Control protocol** parameter to Random access write.

Data Types: Boolean

#### **Parameters**

#### **Control protocol** — Protocol interface selection

Data stream (default) | Pixel stream | Random access read | Random access write

Specify the protocol interface as one of these values:

- Data stream Use this protocol if you require AXI4 data stream.

- Pixel stream Use this protocol if you require AXI4 video stream.

- Random access read Use this protocol if you require AXI4 read.

- Random access write Use this protocol if you require AXI4 write.

The output ports of the block vary based on the type of **Control protocol** and **Control type** that you select. For more details, see "Description" on page 1-8.

#### **Control type** — Control type selection

Valid (default) | Ready

Specify the type of control.

The output ports of the block vary based on the type of **Control protocol** and **Control type** that you select. For more details, see "Description" on page 1-8.

## **Version History**

Introduced in R2019a

## **Extended Capabilities**

#### **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

To automatically generate HDL code for your design, and execute on an SoC device, use the SoC Builder tool. See "Generate SoC Design".

#### **Fixed-Point Conversion**

Design and simulate fixed-point systems using Fixed-Point Designer™.

#### See Also

SoC Bus Creator

## Stream FIFO

Control backpressure between hardware logic and upstream data interface

#### Libraries:

SoC Blockset / Hardware Logic Connectivity

#### **Description**

The Stream FIFO block controls the backpressure from the hardware logic to the upstream data interface. It also controls the flow between the upstream and downstream data interfaces of the hardware logic. Integrate this block as a configurable first-in, first-out (FIFO) block for AXI4 data stream applications. The block enables you to configure its depth and set its almost full threshold value.

#### **Ports**

#### Input

dataIn — Input stream data

scalar

Input stream data from the data source. Specify this value as a scalar.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

dValidIn — Indication of valid input stream data

Boolean scalar

Control signal that indicates if the input stream data from the data source is valid. When this value is 1 (true), the block accepts the values on the **dataIn** port. When this value is 0 (false), the block ignores the values on the **dataIn** port.

Data Types: Boolean

**rdyFromDown** — Ready signal from downstream interface

Boolean scalar

Control signal that indicates if the block can send stream data to the downstream interface. When this value is 1 (true), the downstream interface is ready, and the block can send the stream data. When this value is  $\theta$  (false), the downstream interface is not ready, and the block cannot send the stream data.

Data Types: Boolean

#### Output

dataOut — Output stream data

scalar

Output stream data to the downstream interface. The data type of this output data is the same as the data type of the input data.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

#### dValidOut — Indication of valid output stream data

Boolean scalar

Control signal that indicates if the output stream data is valid. When this value is 1 (true), the output stream data on the **dataOut** port is valid. When this value is  $\theta$  (false), the output stream data on the **dataOut** port is not valid.

Data Types: Boolean

#### **rdyToUp** — Ready signal to upstream interface

Boolean scalar

Control signal that indicates if the block is ready to receive stream data from the upstream interface. When this value is 1 (true), the block is ready to accept stream data from the upstream interface. When this value is 0 (false), the block is not ready to accept stream data from the upstream interface.

Data Types: Boolean

#### **Parameters**

#### **Depth of FIFO** — FIFO depth

16 (default) | positive integer

Specify the depth of the FIFO. This value must be a positive integer and is the maximum number of entries that can be buffered before data gets dropped.

#### Almost full threshold — Almost full threshold value

8 (default) | positive integer

Specify a value that asserts a back-pressure signal from the block to the data source.

To avoid dropping data, set a value allowing the data source enough time to react to backpressure. This value must be a positive integer and smaller than the FIFO depth.

## **Version History**

Introduced in R2019a

#### **Extended Capabilities**

#### **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

## **Fixed-Point Conversion**

Design and simulate fixed-point systems using Fixed-Point Designer  $^{\text{\tiny TM}}$ .

## See Also

Video Stream FIFO

## **Video Stream FIFO**

Control backpressure between hardware logic and upstream video interface

#### Libraries:

SoC Blockset / Hardware Logic Connectivity

## **Description**

The Video Stream FIFO block controls the back-pressure from the hardware logic to the upstream video interface. It also controls the flow between the upstream and downstream pixel data interfaces of hardware logic. Integrate this block as a configurable first-in, first-out (FIFO) block for AXI4 video stream applications. The block enables you to configure its depth and set its almost full threshold value.

#### **Ports**

#### Input

pixelIn — Input pixel data

scalar

Input pixel data from the data source. Specify this value as a scalar.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

ctrlin — Control signals accompanying input pixel data

pixelcontrol bus

Control signals accompanying the pixel stream, specified as a pixelcontrol bus containing five signals. The signals describe the validity of the pixel and its location in the frame.

Data Types: pixelcontrol

**rdyFromDown** — Ready signal from downstream interface

Boolean scalar

Control signal that indicates if the block can send pixel data to the downstream interface. When this value is 1 (true), the downstream interface is ready, and the block can send the pixel data. When this value is  $\theta$  (false), the downstream interface is not ready, and the block cannot send the pixel data.

Data Types: Boolean

#### Output

**pixelOut** — Output pixel data

scalar

Output pixel data to the downstream interface. The data type of this output data is the same as the data type of the input data.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

#### **ctrlOut** — Control signals accompanying output pixel data

pixelcontrol bus

Control signals accompanying output pixel stream, returned as a pixelcontrol bus containing five signals. The signals describe the validity of the pixel and its location in the frame.

Data Types: pixelcontrol

#### **rdyToUp** — Ready signal to upstream interface

Boolean scalar

Control signal that indicates if the block is ready to receive pixel data from the upstream interface. When this value is 1 (true), the block is ready to accept pixel data from the upstream interface. When this value is  $\theta$  (false), the block is not ready to accept pixel data from the upstream interface.

Data Types: Boolean

#### **Parameters**

#### **Depth of FIFO** — FIFO depth

16 (default) | positive integer

Specify the depth of the FIFO. This value must be a positive scalar integer and is the maximum number of entries that can be buffered before data gets dropped.

#### Almost full threshold — Almost full threshold value

8 (default) | positive integer

Specify a value that asserts a back-pressure signal from the block to the data source.

To avoid dropping data, set a value allowing the data source enough time to react to backpressure. This value must be a positive integer and smaller than the FIFO depth.

## **Version History**

Introduced in R2019a

## **Extended Capabilities**

#### **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

#### **Fixed-Point Conversion**

Design and simulate fixed-point systems using Fixed-Point Designer™.

## See Also

Stream FIFO

## **Video Stream Connector**

Connect two IPs with video streaming interfaces

#### Libraries:

SoC Blockset / Hardware Logic Connectivity

## **Description**

The Stream Connector block connects two IPs with video streaming interfaces. Use this block in the FPGA model of an SoC application to connect two IPs.

#### **Ports**

#### Input

wrData — Input video data

scalar

Input video data from the data source. Specify this value as a scalar.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

**wrCtrlin** — Input control signals accompanying pixel stream pixelControl bus

Control signals accompanying the pixel stream, specified as a pixelcontrol bus containing five signals. The signals describe the validity of the pixel and its location in the frame. For additional information about the pixelcontrol bus type, see "AXI4-Stream Video Interface".

Data Types: pixelcontrol

**rdCtrlin** — Ready signal from downstream interface

boolean scalar

Control signal that indicates if the block can send video data to downstream interface. When this value is (true), the downstream block is ready to receive data.

#### Output

rdData — Output video data

scalar

Output video data to the downstream destination IP.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

$\begin{tabular}{ll} \textbf{rdCtrlOut} & - \textbf{Output control signals accompanying output pixel stream} \\ \textbf{pixelcontrol bus} \end{tabular}$

Control signals accompanying the output video data, specified as a pixelcontrol bus containing five signals. The signals describe the validity of the pixel and its location in the frame.

Data Types: pixelcontrol

wrCtrlOut — Ready signal to the upstream interface

boolean scalar

Control signal that indicates that the block can receive stream data from upstream interface.

Data Types: Boolean

## **Version History**

Introduced in R2019a

## **Extended Capabilities**

#### **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

#### **Fixed-Point Conversion**

Design and simulate fixed-point systems using Fixed-Point Designer™.

#### See Also

Stream Connector

## **Stream Connector**

Connect two IPs with data streaming interfaces

#### Libraries:

SoC Blockset / Hardware Logic Connectivity

## **Description**

The Stream Connector block connects two IPs with data streaming interfaces. Use this block in the FPGA model of an SoC application to connect two IPs.

#### **Ports**

#### Input

wrData — Input stream data

scalar

Input stream data from the data source. Specify this value as a scalar.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

wrValid — Indication of valid input stream data

boolean scalar

Control signal that indicates if the input data from the data source is valid. When this value is (true), the block accepts the values on the **wrData** port. When this value is (false), the block ignores the value on the **wrData** port.

Data Types: Boolean

wrLast — Indication of last beat in burst

boolean scalar

Control signal that indicates the last beat of data from the upstream IP.

Data Types: Boolean

**rdReady** — Ready signal from downstream interface

boolean scalar

Control signal that indicates if the block can send stream data to the downstream interface. When this value is (true), the downstream block is ready to receive data.

Data Types: Boolean

#### **Output**

#### rdData — Output stream data

scalar

#### Output stream data to the downstream destination IP.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

#### rdValid — Indication of valid output stream data

boolean scalar

Control signal that indicates if the output stream data is valid.

Data Types: Boolean

#### rdLast — Indicates last beat in burst

boolean scalar

Control signal that indicates that the output stream data now has last beat of burst data.

Data Types: Boolean

#### wrReady — Ready signal to upstream interface

boolean scalar

Control signal that indicates if the block can receive stream data from the upstream interface.

Data Types: Boolean

## **Version History**

Introduced in R2019a

## **Extended Capabilities**

#### **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

#### **Fixed-Point Conversion**

Design and simulate fixed-point systems using Fixed-Point Designer™.

#### See Also

Video Stream Connector

## **DIP Switch**

Connect signals attached to DIP switches on hardware board

#### Libraries:

SoC Blockset / Hardware Logic I/O

#### **Description**

The DIP Switch block controls the hardware logic. The hardware logic signals connected to a DIP Switch block are equivalent to the signals connected to the dual inline package (DIP) switches on the hardware board.

#### **Ports**

#### Input

**DSIn***x* — Input signal

Boolean scalar

Input signal to control the hardware logic. Using this port, you can dynamically control the hardware logic during simulation at run time. Each DIP switch has a port, named **DSIn1** to **DSInx**, where x is **Number of DIP switches**.

#### **Dependencies**

To enable this port, set the **Specify DIP switches via** parameter to InputPort.

Data Types: Boolean

#### Output

DSx — Output signal

Boolean scalar

Output signal that returns the state of the switch. Each DIP switch has a port, named **DS1** to **DSx**, where x is **Number of DIP switches**.

Data Types: Boolean

#### **Parameters**

#### **Hardware board** — View selected hardware

None (default) | Supported Xilinx® or Intel ® boards | Custom boards

This parameter is read-only. To choose a hardware board and configure board parameters, see "Hardware Implementation Pane" on page 2-2.

#### **View DIP switches location** — View DIP switches

button

To view a diagram with the location of the DIP switches on the selected hardware board, click the **View DIP switches location** button.

This button is enabled only when you select specific Xilinx or Intel boards. For more information about these boards, refer to "Supported Third-Party Tools and Hardware".

#### **IO logic** — IO logic indicator

None (default) | Active High | Active Low

This parameter is read-only. Indicates the IO logic level on the selected hardware board.

When the **IO logic** parameter is shown as **Active Low**, the DIP Switch block accepts and outputs active low signals when you set the **Specify DIP switches via** parameter to **InputPort** and outputs active low signals when you set the **Specify DIP switches via** parameter to **Dialog**. The block represents these port names prefixed with letter n. For example, **nDS1**.

#### **Specify DIP switches via** — DIP switch source

Dialog (default) | InputPort

To control the hardware logic by using the block parameters, select Dialog. To control the hardware logic from the input port, select InputPort.

#### **Number of DIP switches** — DIP switch selection

1 (default) | list of integers in the range [1, n]

To specify the required number of DIP switch ports, select a value from the **Number of DIP switches** list. *n* represents the number of available DIP switches on the specified hardware board. For example, if you select 3 from the list, the block shows three DIP switch ports.

To use only the nth DIP switch, set the **Number of DIP switches** parameter to n and terminate the unused DIP switch ports.

#### **DS***n* — Selected DIP switches

Off (default) | On

To enable the nth DIP switch port, select 0n for the DSn parameter. n represents the number of available DIP switches on the specified hardware board.

#### **Dependencies**

To enable this parameter, set the **Specify push buttons via** parameter to Dialog.

#### Sample time — System sample time

-1 (default) | positive scalar

Specify the time interval a DIP switch toggles between On and Off.

## **Version History**

Introduced in R2019a

## **Extended Capabilities**

#### **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

#### **Fixed-Point Conversion**

Design and simulate fixed-point systems using Fixed-Point Designer<sup>™</sup>.

#### **See Also**

LED | Push Button

## **12C Master**

Configure and communicate with I2C slave device

#### Libraries:

SoC Blockset / Hardware Logic I/O

## **Description**

The I2C Master block configures and communicates with an inter-integrated circuit communications (I2C) slave device connected to a field programmable gate array (FPGA). This block contains an I2C master controller with an AXI-Lite interface to perform the configuration.

The I2C Master block supports these features:

- AXI4-Lite interface support for configuration and access

- Single-master and multi-slave support

- Support 7-bit and 10-bit address I2C slave devices

- Burst mode support with a maximum burst size of 256 bytes

- Support multiple transmission speed modes

- An HDL-IP compatible model with code generation capability

The block uses the AXI-Lite interface to configure and create a control path interface to communicate with an I2C slave device. The hardware generated from the generation process contains an AXI-Lite register interface and two hardware interfaces, serial clock (SCL), and serial data (SDA). SCL and SDA connect the I2C Master block and the slave device.

Each port represented in the block is an AXI-Lite register, except the **sdaIn**, **sclIn**, **scl**, and **sda** ports. To communicate with a slave device, the AXI-Lite register interface configures the register information in the I2C Master block. This table contains the I2C Master AXI-Lite register information.

| Register Address |                               | Register Size in Bits | Operation Mode |

|------------------|-------------------------------|-----------------------|----------------|

| 0x100            | ctrlInf — Control information | 32                    | Write          |

| 0x104            | slvAddr — Slave address       | 32                    | Write          |

| 0x108            | regAddr — Register<br>address | 32                    | Write          |

| 0x10C            | dataReg — Data register       | 32                    | Write          |

| Register Address | Port and Register Name                         | Register Size in Bits | Operation Mode |

|------------------|------------------------------------------------|-----------------------|----------------|

| 0x110            | readDone — Read done register                  | 32                    | Write          |

| 0x114            | done — Done register                           | 32                    | Write          |

| 0x118            | rdy — Ready register                           | 32                    | Read           |

| 0x11C            | <b>respData</b> — First response data register | 32                    | Read           |

| 0x120            | validData — Response data<br>valid register    | 32                    | Read           |

| 0x124            | statusReg — Status<br>register                 | 32                    | Read           |

To perform read and write operations using the I2C Master block, you need to follow a proper sequence. This section provides information about the sequence flow for read and write operations.

#### **Read Sequence**

To read data from an external slave device:

- **1** Send the **ctrlInf** register information.

- 2 Send the **slvAddr** register information.

- **3** Send the **regAddr** register information.

- Set the **done** register to 1 after sending one set of register information to the block and then set it to 0.

- Read the response data from the external slave device. After reading the data from the **respData** register, set the **readDone** register to 1 and then set it to θ immediately.

- Set the **readDone** register to 1 again, to read more than 4 bytes of data. After the read operation, set it to 0 immediately.

In read sequence, one set of register information is a combination of **ctrlInf**, **slvAddr**, and **regAddr** registers.

#### **Write Sequence**

To write data to an external slave device:

- **1** Send the **ctrlInf** register information.

- 2 Send the **slvAddr** register information.

- **3** Send the **regAddr** register information.

- 4 Send the **dataReg** register that contains the data to write to the slave device register.

- Set the **done** register to 1 after writing one set of register information to the block, and then set it to 0.

- Set the **done** register to 1 again, to write more than 4 bytes of data. After the write operation, set it to  $\theta$  immediately.

In write sequence, one set of register information is a combination of **ctrlInf**, **slvAddr**, **regAddr**, and **dataReg** registers.

#### **Ports**

#### Input

**ctrlinf** — Control information

scalar

Control information register contains configuration information on how the block communicates with the slave device, specified as a scalar. This register is a combination of read or write operation indication bit, number of bytes of slave-device register address, number of bytes of slave-device data register, and slave device address type bit. You can modify the configuration based on your requirement.

| Bit   | Purpose                                                | Value Description                                                                                                                                                                                                                                                              |

|-------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Set write or read mode.                                | To write to the slave-device register, set this value to 0. To read from the slave-device register, set this value to 1.                                                                                                                                                       |

| [2:1] | Set the size of the slave-<br>device register address. | <ul> <li>If the slave-device register address size is:</li> <li>One byte (8 bits), set this value to 00</li> <li>Two bytes (16 bits), set this value to 01</li> <li>Three bytes (24 bits), set this value to 10</li> <li>Four bytes (32 bits), set this value to 11</li> </ul> |

| Bit    | Purpose                                         | Value Description                                                                                                            |

|--------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| [10:3] | Set the data size of the slave-device register. | If the slave-device register supports:                                                                                       |

|        |                                                 | One byte of data, set this value to 00000000                                                                                 |

|        |                                                 | • Two bytes of data, set this value to 00000001                                                                              |

|        |                                                 | Three bytes of data, set this value to 00000010                                                                              |

|        |                                                 | • Four bytes of data, set this value to 00000011                                                                             |

|        |                                                 | • Five bytes of data, set this value to 00000100                                                                             |

|        |                                                 | Six bytes of data, set this value to 00000101                                                                                |

|        |                                                 | Seven bytes of data, set this value to 00000110                                                                              |

|        |                                                 | • Eight bytes of data, set this value to 00000111                                                                            |

|        |                                                 | Nine bytes of data, set this value to 00001000                                                                               |

|        |                                                 | • Ten bytes of data, set this value to 00001001                                                                              |

|        |                                                 | • Eleven bytes of data, set this value to 00001010                                                                           |

|        |                                                 | Twelve bytes of data, set this value to 00001011                                                                             |

|        |                                                 | Thirteen bytes of data, set this value to 00001100                                                                           |

|        |                                                 | • Fourteen bytes of data, set this value to 00001101                                                                         |

|        |                                                 | • Fifteen bytes of data, set this value to 00001110                                                                          |

|        |                                                 | • Sixteen bytes of data, set this value to 00001111                                                                          |

|        |                                                 |                                                                                                                              |

|        |                                                 | 256 bytes of data, set this value to 11111111                                                                                |

| 11     | Set the slave device type                       | To configure 7-bit address slave device, set this value to 0. To configure 10-bit address slave device, set this value to 1. |

Data Types: uint16

## $\textbf{slvAddr} - \mathsf{Slave} \ \mathsf{address}$

scalar

Slave-address register that contains the address of the slave device, specified as a scalar.

Data Types: uint16

#### regAddr — Register address

scalar

Register address of the slave device, specified as a scalar.

Data Types: uint32

#### dataReg — Data register

scalar

Data register, specified as a scalar. The block uses this port to write data to the slave-device register.

Data Types: uint32

#### readDone — Read done signal

Boolean scalar

Read done signal, specified as a Boolean scalar. When this value is 1 (true), the user is ready to read the response data from the block that is received from the slave device. When this value is  $\theta$  (false), the user is not ready to read the response data from the block.

Data Types: Boolean

#### done — Done signal

Boolean scalar

Done signal, specified as a Boolean scalar. This value indicates the block when to read the AXI-Lite register information.

Data Types: Boolean

#### sdaIn — Input serial data

Boolean scalar

Input serial data, returned as a Boolean scalar. This port provides a serial data signal to the block from the slave device.

Data Types: Boolean

#### **sclin** — Input serial clock

Boolean scalar

Input serial clock, returned as a Boolean scalar. This port provides a serial clock signal to the block from the slave device.

Data Types: Boolean

#### Output

#### scl — Output serial clock

Boolean scalar

Output serial clock, specified as a Boolean scalar. This port provides a serial clock signal from the block to the slave device.

Data Types: Boolean

#### sda — Output serial data

Boolean scalar

Output serial data, specified as a Boolean scalar. This port provides a serial data signal from the block to the slave device.

Data Types: Boolean

### rdy — Ready signal

Boolean scalar

Ready signal, returned as a Boolean scalar. When this value is 1 (true), the block is ready to accept the configuration data. When this value is 0 (false), the block is not ready to accept the configuration data.

Data Types: Boolean

### **respData** — Response data register

scalar

Response data register containing the data from the slave-device register, returned as a scalar.

Data Types: uint32

### **validData** — Indication of valid response data

Boolean scalar

Control signal that indicates if the response data is valid, returned as a Boolean scalar. When this value is 1 (true), the response data from response data registers is valid. When this value is 0 (false), the response data from response data registers is not valid.

Data Types: Boolean

### **statusReg** — I2C bus status indicator

scalar

Indicates the status of the I2C bus, returned as a scalar.

| Bit   | Purpose                                                                      | Value Description                                                                                                                                                                       |

|-------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:4] | Reserved                                                                     | Reserved                                                                                                                                                                                |

| 3     | Indicates the status of the I2C bus.                                         | When this value is 1, it indicates that the I2C bus is busy. When this value is 0, it indicates that the I2C bus is idle and ready for configuration.                                   |

| 2     | Indicates the acknowledgment status from the slave device to the I2C Master. | When this value is 1, it indicates that the slave device has not acknowledged the I2C Master. When this value is 0, it indicates that the slave device has acknowledged the I2C Master. |

| [1:0] | Reserved                                                                     | Reserved                                                                                                                                                                                |

Data Types: uint32

### **Parameters**

### **Speed** — Speed-mode selection

Standard Mode (default) | Fast Mode | Fast Plus Mode

Specify the speed mode as one of these values:

- Standard Mode Supports frequencies up to 100 KHz

- Fast Mode Supports frequencies up to 400 KHz

- Fast Plus Mode Supports frequencies up to 1 MHz

### **Version History**

Introduced in R2019a

R2020a: I2C Master block has one data register input port and one data register output

Behavior changed in R2020a

In R2019a, the I2C Master block has input data register ports dataReq, dataReq1, dataReq2, and dataReg3 and output response data register ports respData, respData1, respData2, and respData3. These data register ports support a maximum of 16 bytes per transaction. In R2020a, these register ports are replaced with single data register ports; input port dataReg and output port respData. Each of these single data register ports support a maximum of 256 bytes per transaction.

In R2020a, Simulink® errors if you open a model that was created in an earlier release and that contains an I2C Master block. In this case, connections to ports dataReg1, dataReg2, dataReg3, respData1, respData2, and respData3 are either missing or reconnected to empty ports on the block. Manually check and update the port connections in your model to proceed further.

### **Extended Capabilities**

### **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

To automatically generate HDL code for your design, and execute on an SoC device, use the SoC Builder tool. See "Generate SoC Design".

### **Fixed-Point Conversion**

Design and simulate fixed-point systems using Fixed-Point Designer<sup>™</sup>.

### **LED**

Connect signals attached to LEDs on hardware board

#### Libraries:

SoC Blockset / Hardware Logic I/O

### **Description**

The LED block indicates the status of a signal. The hardware logic signals connected to an LED block are equivalent to the signals connected to the light emitting diodes (LED) on the hardware board.

### **Ports**

### Input

**LED***x* — Input signal

Boolean scalar

Input signal from the hardware logic. Each LED has a port, named **LED1** to **LEDx**, where **x** is **Number of LEDs**.

Data Types: Boolean

### **Parameters**

### **Hardware board** — View selected hardware

None (default) | Supported Xilinx or Intel boards | Custom boards

This parameter is read-only. To choose a hardware board and configure board parameters, see "Hardware Implementation Pane" on page 2-2.

#### **View LEDs location** — View LEDs

button

To view a diagram of the location of the LEDs on the selected hardware board, click the **View LEDs location** button.

This button is enabled only when you select specific Xilinx or Intel boards. For more information about these boards, refer to "Supported Third-Party Tools and Hardware".

### **IO logic** — IO logic indicator

None (default) | Active High | Active Low

This parameter is read-only. Indicates the IO logic level on the selected hardware board.

When the **IO logic** parameter is shown as **Active Low**, the LED block accepts active low signals and represents the port names prefixed with letter *n*. For example, **nLED1**.

### **Number of LEDs** — Number of LED ports

1 (default) | list of integers in the range [1, n]

Specify the required number of LED ports by specifying a value from this list. n is the number of available LEDs on the specified hardware board. For example, if you set this parameter to 4, the block shows four LED ports.

To use only the nth LED, set the **Number of LEDs** parameter to n and leave the unused LED ports unconnected.

For the Zynq® UltraScale+™ RFSoC ZCU216 Evaluation Kit, the first three LED ports represent the first set of red, green, and blue (RGB) LEDs out of the eight available sets, the next three LED ports represent the second set of RGB LEDs, and so on. For example, if you set the **Number of LEDs** parameter to 9, the **LED1**, **LED4**, and **LED7** ports connect to the red LEDs, the **LED2**, **LED5**, and **LED8** ports connect to the green LEDs, and the **LED3**, **LED6**, and **LED9** ports connect to the blue LEDs on the ZCU216 evaluation board.

## **Version History**

Introduced in R2019a

### **Extended Capabilities**

#### **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

#### **Fixed-Point Conversion**

Design and simulate fixed-point systems using Fixed-Point Designer™.

### See Also

DIP Switch | Push Button

### **Push Button**

Connect signals attached to push buttons on hardware board

#### Libraries:

SoC Blockset / Hardware Logic I/O

### **Description**

The Push Button block controls the hardware mechanism. The hardware logic signals connected to a Push Button block are equivalent to the signals connected to the push buttons on the hardware board.

### **Ports**

### Input

### **PBInx** — Input signal

Boolean scalar

Input signal to control the hardware logic. Using these ports, you can dynamically control the hardware logic during simulation at run time. Each push button has a port, named **PBIn1** to **PBInx**, where *x* is **Number of push buttons**.

### **Dependencies**

To enable this port, set the **Specify push buttons via** parameter to InputPort.

Data Types: Boolean

### Output

### **PB**x — Output signal

Boolean scalar

Output signal that returns the state of the push button. Each push button has a port, named **PB1** to **PB***x*, where *x* is **Number of push buttons**.

Data Types: Boolean

### **Parameters**

### **Hardware board** — View selected hardware

None (default) | Supported Xilinx or Intel boards | Custom boards

This parameter is read-only. To choose a hardware board and configure board parameters, see "Hardware Implementation Pane" on page 2-2.

### **View push buttons location** — View push buttons

button

To view a diagram of the location of the push buttons on the selected hardware board, click the **View push buttons location** button.

This button is enabled only when you select specific Xilinx or Intel boards. For more information about these boards, refer to "Supported Third-Party Tools and Hardware".

### **IO logic** — IO logic indicator

None (default) | Active High | Active Low

This parameter is read-only. Indicates the IO logic level on the selected hardware board.

When the **IO logic** parameter is shown as **Active Low**, the Push Button block accepts and outputs active low signals when you set the **Specify push buttons via** parameter to **InputPort** and outputs active low signals when you set the **Specify push buttons via** parameter to **Dialog**. The block represents these port names prefixed with letter n. For example, **nPB1**.

### **Specify push buttons via** — Push-button source

Dialog (default) | InputPort

To control the hardware logic by using the block parameters, select Dialog. To control the hardware logic from the input port, select InputPort.

### **Number of push buttons** — Push-button selection

1 (default) | list of integers in the range [1, n]

To specify the required number of push-button ports, select a value from the **Number of push buttons** list. *n* represents the number of available push buttons on the specified hardware board. For example, if you select 3 from the list, the block shows three push-button ports.

To use only the nth push button, set the **Number of push buttons** parameter to n and terminate the unused push button ports.

### **PB***n* — Selected push buttons

Off (default) | On

To enable the nth push-button port, select 0n for the PBn parameter. n represents the number of available push buttons on the specified hardware board.

### **Dependencies**

To enable this parameter, set the **Specify push buttons via** parameter to Dialog.

### **Sample time** — Sampling interval

-1 (default) | positive scalar

Specify the time interval a push button toggles between On and Off.

# **Version History**

Introduced in R2019a

### **Extended Capabilities**

### **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

To automatically generate HDL code for your design, and execute on an SoC device, use the **SoC Builder** tool. See "Generate SoC Design".

### **Fixed-Point Conversion**

Design and simulate fixed-point systems using Fixed-Point Designer™.

### **See Also**

DIP Switch | LED

### **AXI4 Master Sink**

Receive random access memory data

#### Libraries:

SoC Blockset / Hardware Logic Testbench

### **Description**

The AXI4 Master Sink block receives random access memory data from AXI4-based data interface blocks. You can use this block as a test sink block for simulating AXI4-based data applications.

The block accepts data along with a control bus and outputs a control bus.

### **Ports**

### Input

rdData — Input data scalar | vector

Input data from the data source. This value must be a scalar or vector.

Before reading the data, set the required data type. To set the data type, see the **Data type** parameter.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

### rdCtrlin — Input control bus

bus

Input control bus from the data producer, specified as a bus. This control bus comprises these control signals:

- rd\_aready Indicates the data source accepted the read request

- rd dvalid Indicates the data returned for the read request is valid

Data Types: ReadControlS2MBus0bj

### Output

### rdCtrlOut — Output control bus

bus

Output control bus to the data source indicating the block is ready to accept data, returned as a scalar. This control bus comprises these control signals:

rd\_addr — Starting address for the read transaction that is sampled at the first cycle of the transaction

- rd len Number of data values you want to read, sampled at the first cycle of the transaction

- rd avalid Control signal that specifies whether the read request is valid

- rd\_dready Control signal that indicates when the block can read data

Data Types: ReadControlM2SBusObj

### **Parameters**

### Data type — Input data type

uint8 (default) | double | single | int8 | int16 | int32 | int64 | uint16 | uint32 | uint64 |

fixed point

Select the data type format for the input AXI data.

Click the button to display the **Data Type Assistant**, which helps you to set the data type for the **rdData** input port. For details, see "Specify Data Types Using Data Type Assistant".

### **Dimensions** — Input data dimensions

1 (default) | positive integer | array

Specify the dimensions of the input data as a positive scalar or an array. This value defines the size of the data signal.

Example: 1 specifies a scalar sample.

Example: [10 1] specifies a vector of ten scalars.

# **Enable sample packing (last signal dimension as channel)** — Pack data on the last dimension of the signal

off (default) | on

Select this parameter to enable data packing across the last dimension of the signal. The Memory Channel block packs the data along the last dimension of the signal. For example, if the channel data type is uint32, the dimensions are [1024 4], and if you select this parameter, then the memory channel generates 1024 read or write transactions of 128 bits. For this example, if you clear this sample packing parameter, the memory channel generates 4096 transactions of 32 bits each.

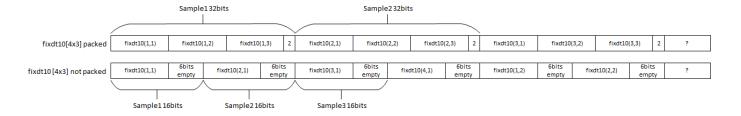

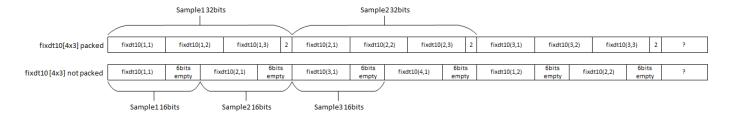

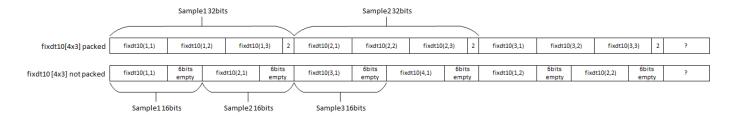

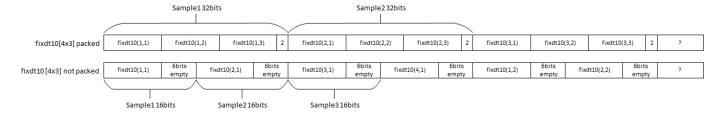

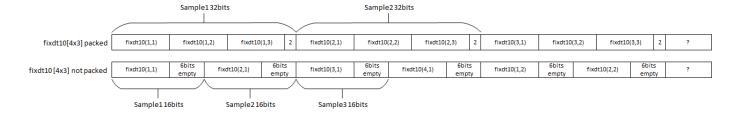

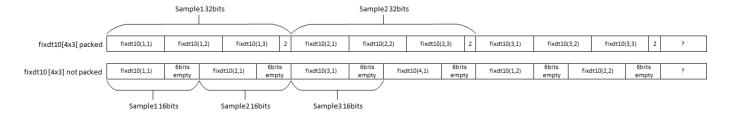

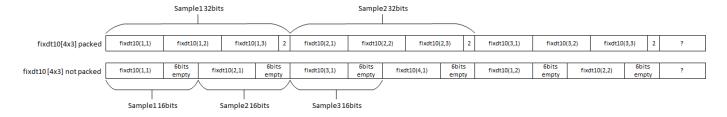

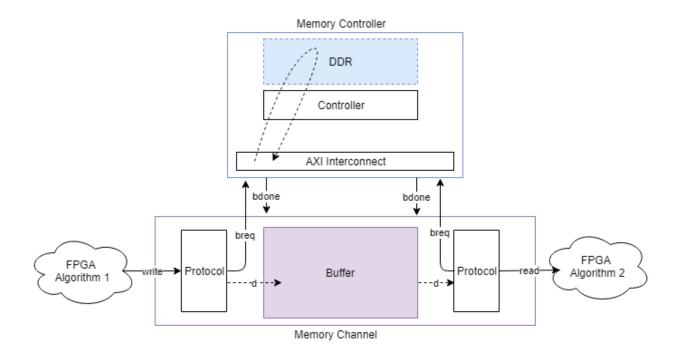

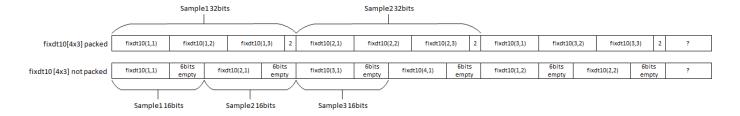

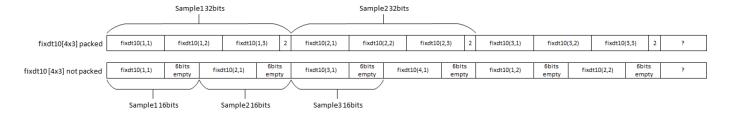

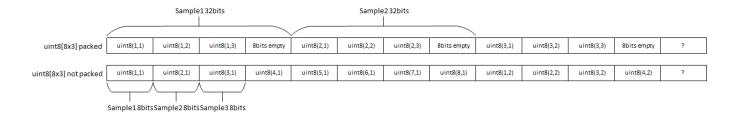

This figure shows how data is aligned for a signal with data type fixdt10[4x3]. When the data is packed, three 10-bit words are concatenated and extended by 2 bits to a 32-bit sample. When the data is not packed, each 10-bit word is extended to a 16-bit sample.

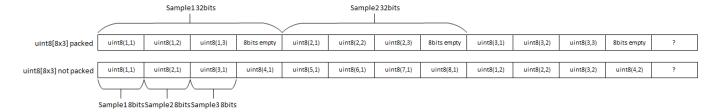

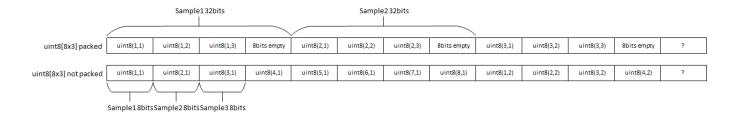

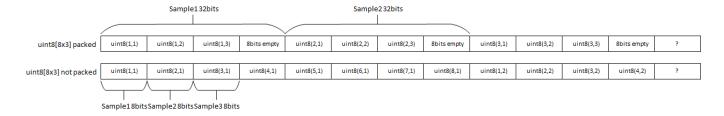

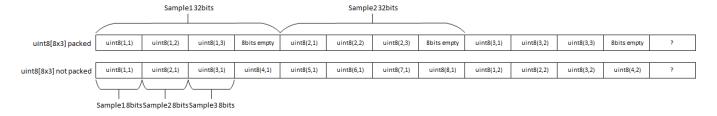

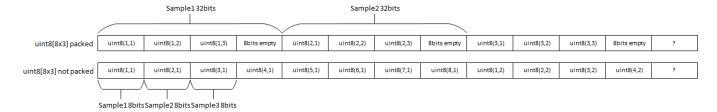

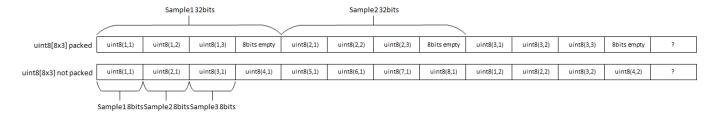

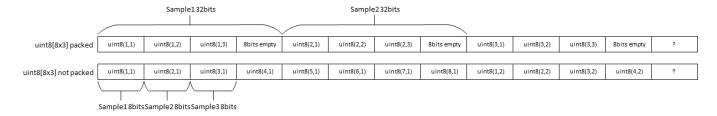

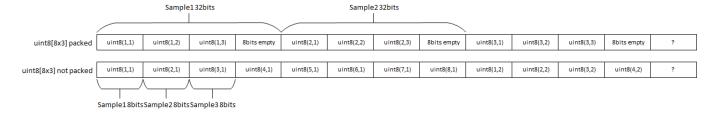

This figure shows how data is aligned for a signal with data type uint8[8x3]. When the data is packed, three 8-bit words are concatenated and extended by 8 bits to a 32-bit sample. When the data is not packed, each 8-bit word is represented as an 8-bit sample.

The combined width of the flattened signal must not exceed 512 bits.

### **Number of transfers** — Number of read requests to send

1 (default) | positive integer

Specify the number of read requests for the block to send.

#### **Initial address** — Start address

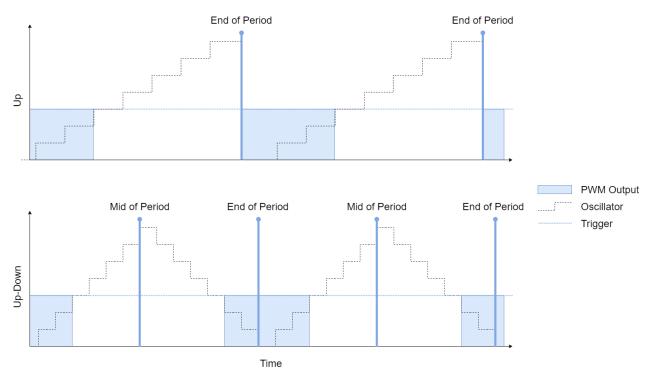

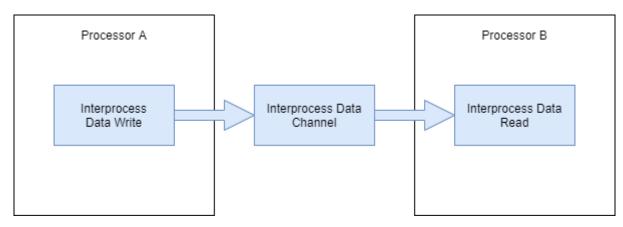

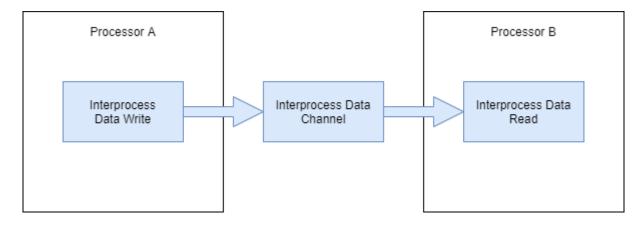

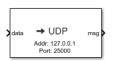

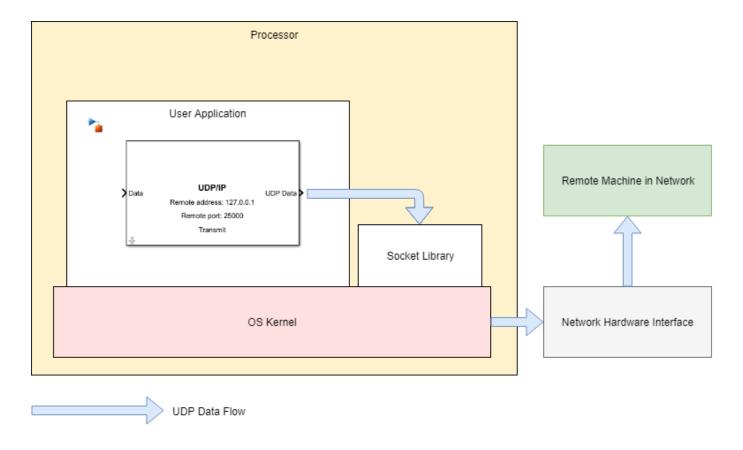

0 (default) | nonnegative scalar integer